1、DAC的16位输入移位寄存器有三种控制模式,其中最高位用于控制模式,中间8位存储数据,其余位无效在编写Verilog配置程序时,主要思路是利用SPI协议,通过时钟SCLK将控制模块的16位数据分时传输到DAC,以便正确驱动DAC输出顶层模块设计应包含对SPI接口的管理和DAC控制,而Testbench则用于创建仿真,通过模拟实际verilog移位寄存器;扰码的原理基于反馈移位寄存器,采用的多项式通常遵循IEEE标准,以确保扰码效果具体实现方面,使用Verilog HDL编写scramblerv文件,构建扰码器模块,实现对输入序列的扰码功能此外,scrambler_tbv文件作为测试台,用于验证scramblerv的正确性,通过仿真验证其性能仿真过程使用ModelSim 107进行,通过每次;EDA综合后,模块转换为电路图,所有代码必须位于模块内,不能在外部编写Verilog语句模块在设计中表示行为特征的实现单元,输入组合产生相应输出重复使用相同模块形成更大模块,提高设计复用性,实现复杂硬件如DFF连接形成移位寄存器设计可以分解为多个模块,如GPU引擎分为子块每个子模块实现特定功能;串并转换很简单,就是移位寄存器,后面最好跟一个锁存器,实现你所要求的功能需要四位移位寄存器和四位锁存器,锁存器的作用就是保持并行数据在移位时不发生变化module shiftnreset,clk,en,in,outinput nreset,clk,en,inoutput 30 outreg 10 count移位计数,控制并行数据;环形数据收发模式下,SPI通过两个移位寄存器实现数据的发送与接收,而数据的深度81632等则决定了每次传输的数据量SPI协议没有规定的时钟频率和结构,但因其简单性灵活性和高数据传输性能,被广泛应用于各种场景,如微控制器传感器液晶显示控制器等在实际应用中,SPI根据外设规格和要求;在数字逻辑设计中,线性反馈移位寄存器Linear Feedback Shift Register, LFSR是一种不可或缺的工具,它以位为单位存储数据,通过抽头和反馈函数实现周期性的状态变化LFSR的核心在于其级数,决定了存储位数和最长循环周期,级数越高,存储位越多,周期也越长,周期的计算公式为\2^n 1\,其中;1 CIC滤波器设计 结构描述CIC滤波器主要由积分器和梳状滤波器组成,通过级联的方式实现抽取滤波其结构简单,硬件实现效率高,适用于高速信号处理 Verilog实现在Verilog中,可以通过移位寄存器和加法器实现积分器和梳状滤波器的功能同时,需要注意抽取操作的实现,即在每级滤波后降低采样率2 HB;Verilog中的循环语句主要包括forwhileforever和repeat,它们的作用和特点如下For循环 作用用于确定次数的迭代特点尽管在FPGA设计中可能部分可综合,但在处理数组或需要固定次数操作时非常实用语法包括设置初始值判断条件和更新变量应用场景例如,通过for循环实现移位寄存器的功能Forever循环。

2、在数字逻辑设计领域,线性反馈移位寄存器LFSR以其独特的性质和应用而受到广泛关注它通过位级别的存储和反馈移位操作,生成具有周期性的二进制序列LFSR的关键特性在于其级数,它决定了寄存器的位数和最长的循环周期,该周期通常表示为\2^n 1\,其中\n\代表寄存器的级数特征多项式是LFSR设;在Verilog编程中,实现小数分频且占空比非50%的方法主要包括以下几点45倍分频设计利用9个参考时钟周期通过设置一个9位移位寄存器,并在每个周期向左循环移位,来生成两个对称的脉冲产生对称脉冲为了确保对称性,需要在第5个计时周期的下降沿采集信号,以产生包含45个周期的两个对称脉冲占空;1 shift reg module shift_4clk,rst,in,outinput clk,rstinput inoutput outwire outreg 30 shiftregalways@posedge clk or negedge rst 异步清零 if!rstshiftreglt=0else begin shiftreg0lt=inshiftreg1lt=shiftreg0shiftreg2lt=shiftreg1shiftreg3lt;例如,要生成一个码长为31的m序列,寄存器级数为5,选择反馈系数456775中的一个,如45,因其反馈线最少,电路最简单45转换为二进制为,表示C5C2C0反馈支路连通,其他断开Verilog HDL程序可用于实现m序列生成仿真波形展示了长度为31的m序列欢迎关注公众号AIShareLab,与verilog移位寄存器我们。

3、module m_sequencesclk,signalinput clkoutput signalreg signalreg c1,c2,c3reg c0=1always@posedge clkbegin c3lt=c2c2lt=c1c1lt=c0c0lt=c3 + c2 signallt=c3end endmodule 具体细节可以看一些关于通原方面的知识,其实就是几个反馈移位寄存器,很简单 就;最后,通过几个移位寄存器的例子,我们可以进一步理解这两种赋值方式在实际电路设计中的应用虽然阻塞赋值方式可以用于描述移位寄存器,但其设计风格和顺序安排必须非常谨慎,以避免竞争和冒险问题相比之下,非阻塞赋值方式在描述时序逻辑时更为稳定和可靠,且在所有设计中都能保证仿真和综合的一致性综上所。

4、构建一个4位的右移逻辑移位寄存器,具备异步复位同步加载和使能功能若加载和使能输入同时被激活1,加载输入具有更高优先级逻辑移位寄存器的工作原理类似于做乘法和除法操作,向左移位相当于乘法,向右移位则为除法接下来,设计一个64位算术移位寄存器,同步加载,支持左右移位,移位位置可选1位。

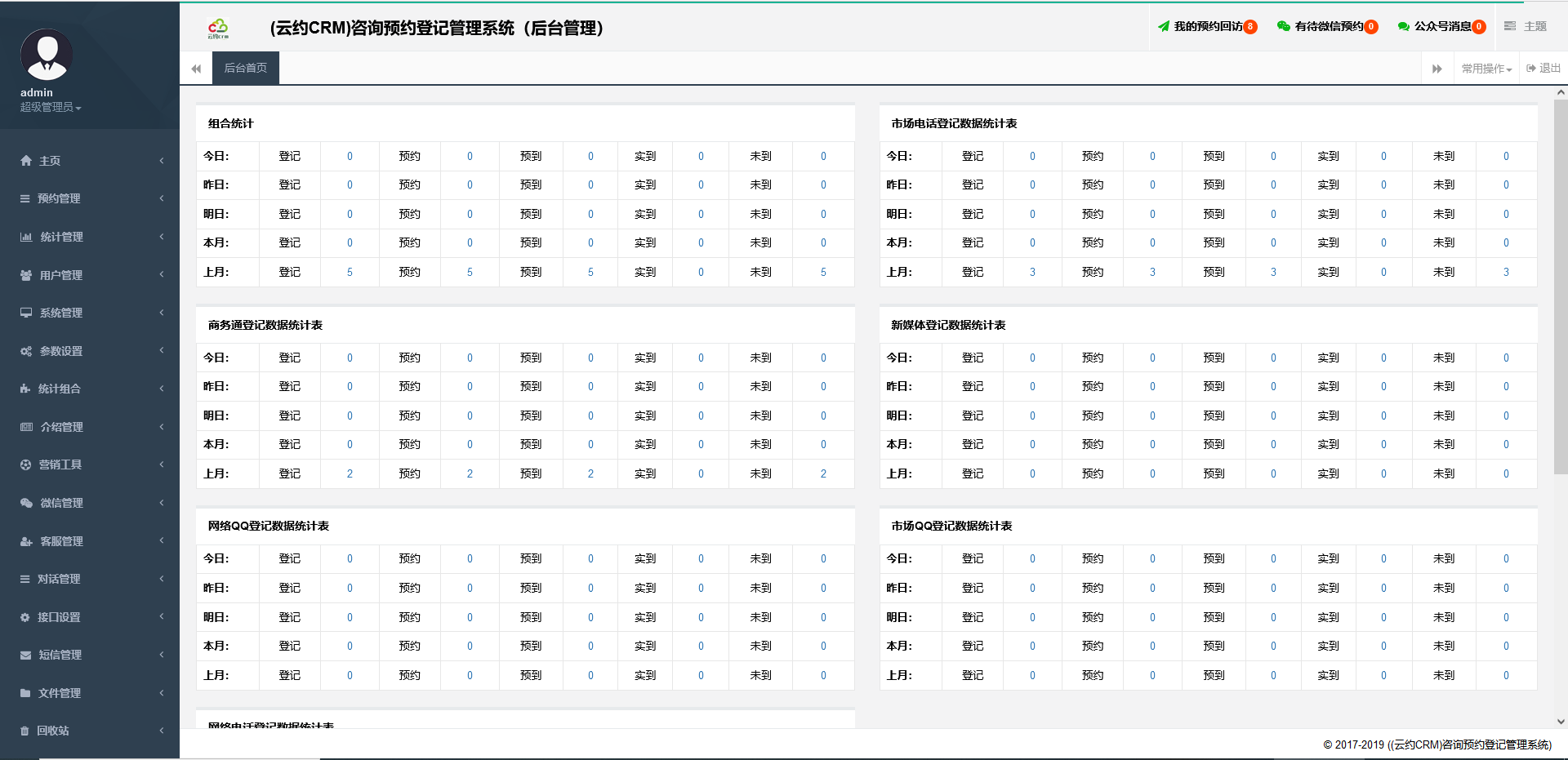

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

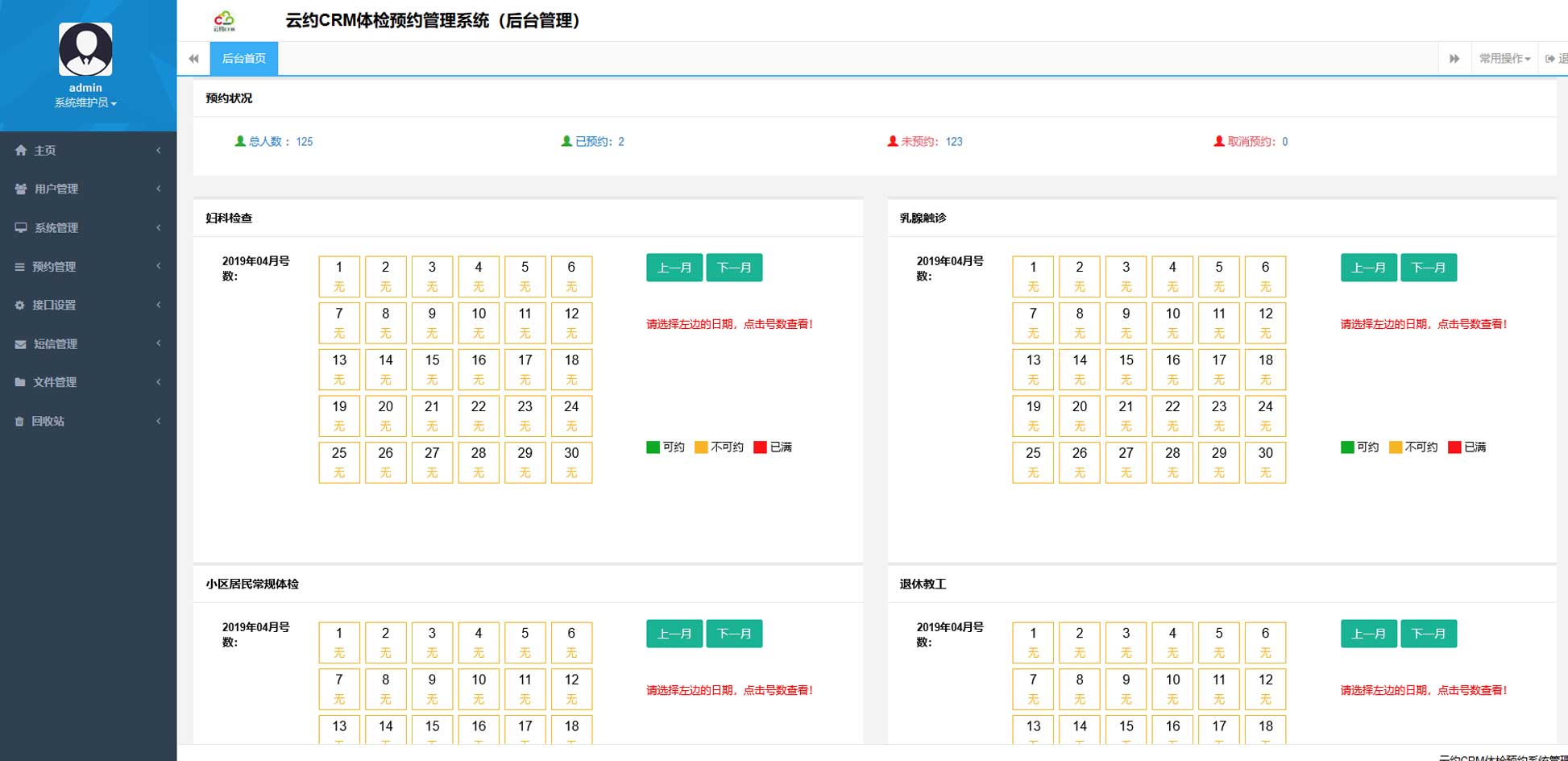

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

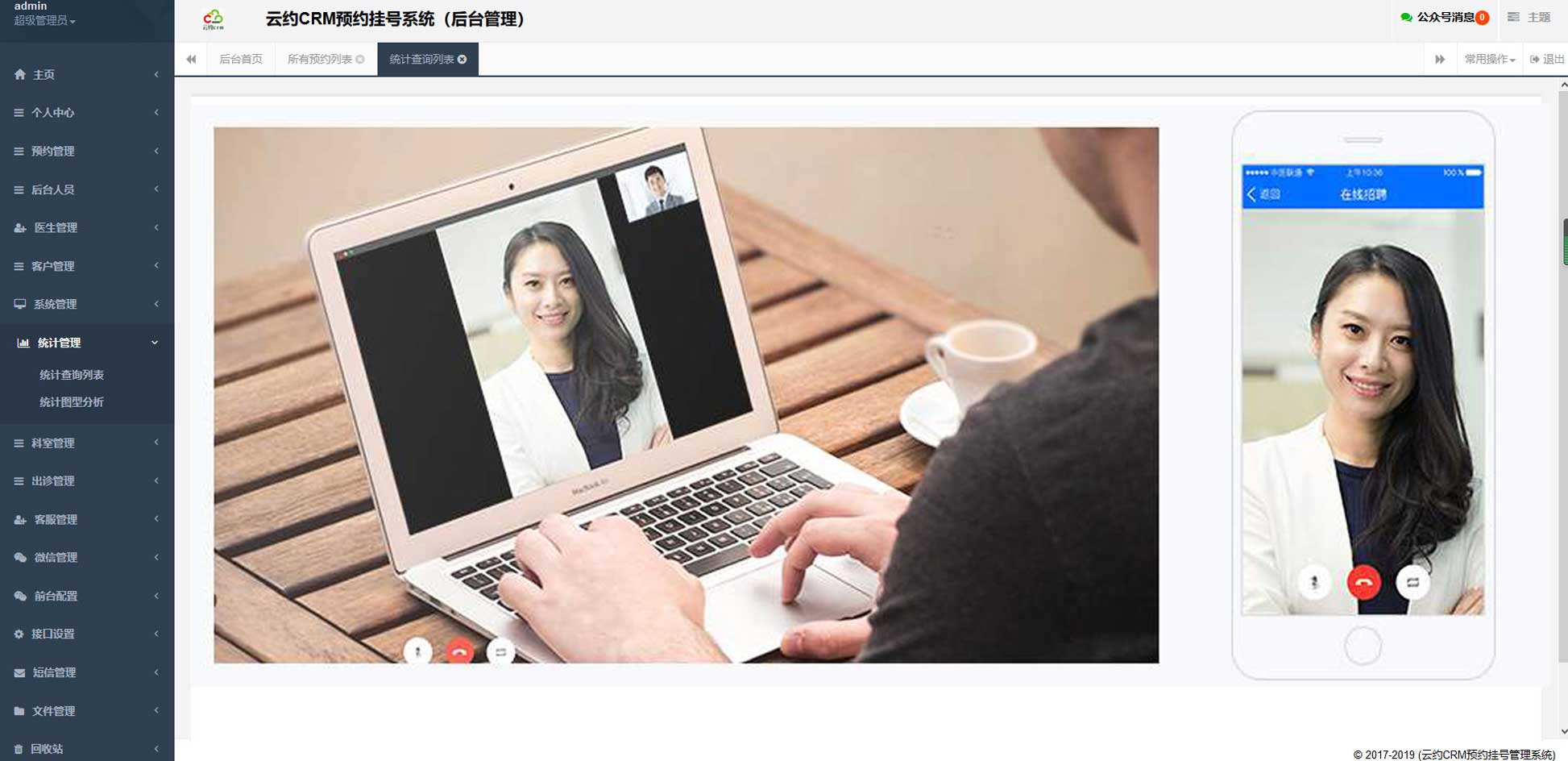

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

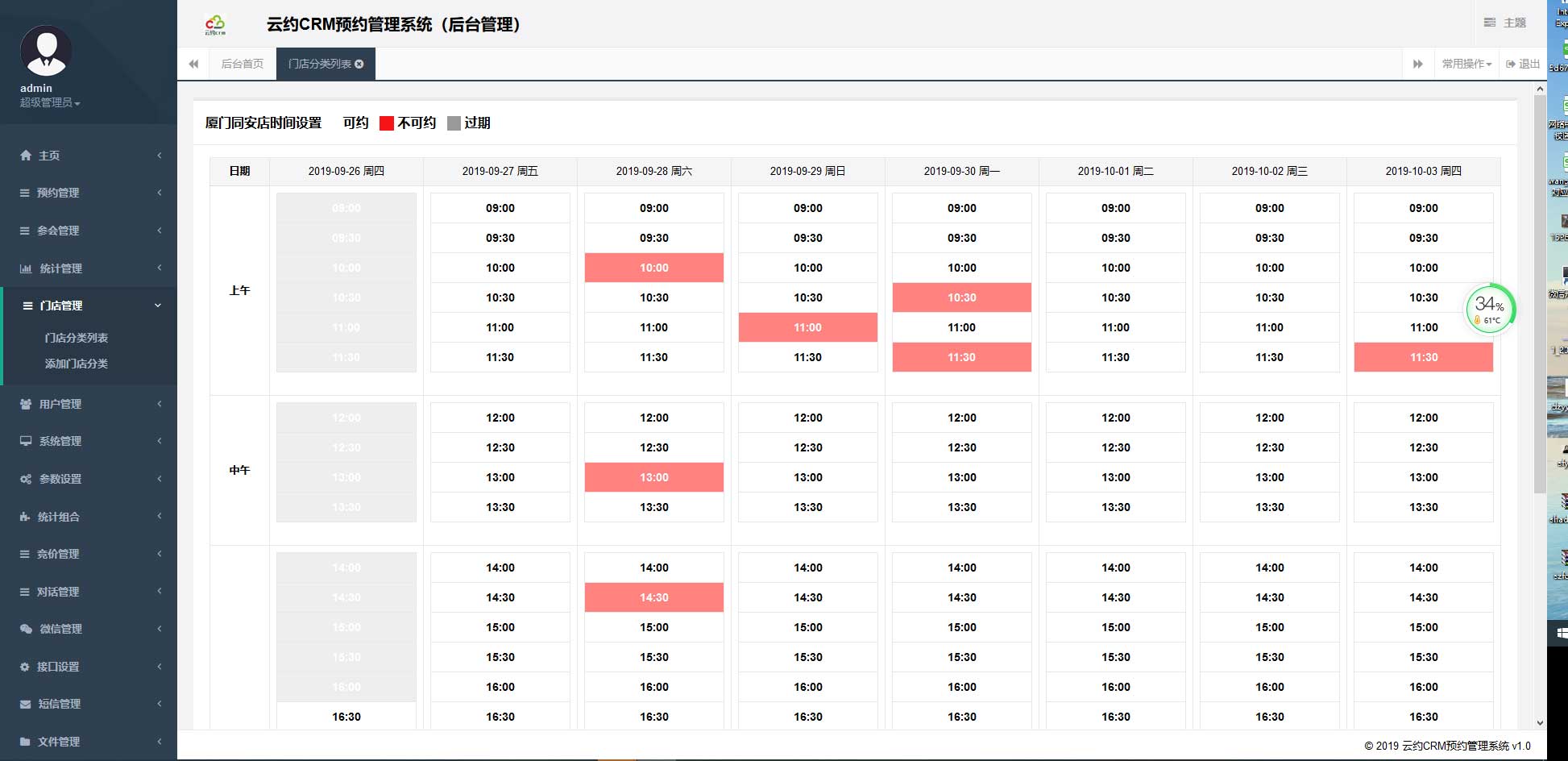

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com