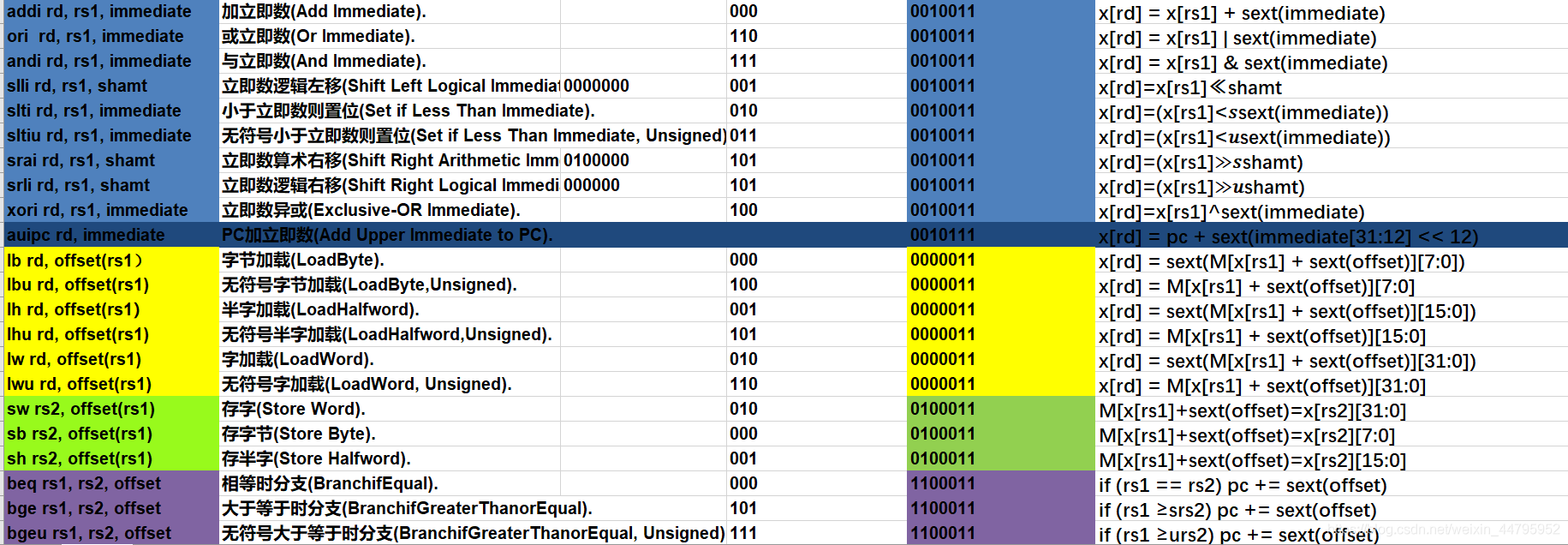

RISCV是一种新的指令集体系结构ISA优秀的VerilogFPGA开源项目介绍(三十六)-RISC-V(新增一),旨在为学术界和工业界提供一个开放免费标准的体系结构其目标是打造一个完全开放的ISA,能够自由使用,且适合直接在硬件上实现,而非仅用于模拟或二进制翻译它避免了对特定微体系结构风格如微编码按序去耦合乱序等或实现技术如全定制ASICFPGA的过度体系。

要深入了解安装步骤,请参考接下来,优秀的VerilogFPGA开源项目介绍(三十六)-RISC-V(新增一)我们以蜂鸟E203为例进行详细说明为了将FPGA变成RISCV开发板,需要烧录蜂鸟E203的比特流首先,您需要下载源码,该源码和RTT固件源码位于同一个仓库中在下载源码后,您需要打开目录Tang_E203_Miniprojecte203egmini_newal中的项目,并生成。

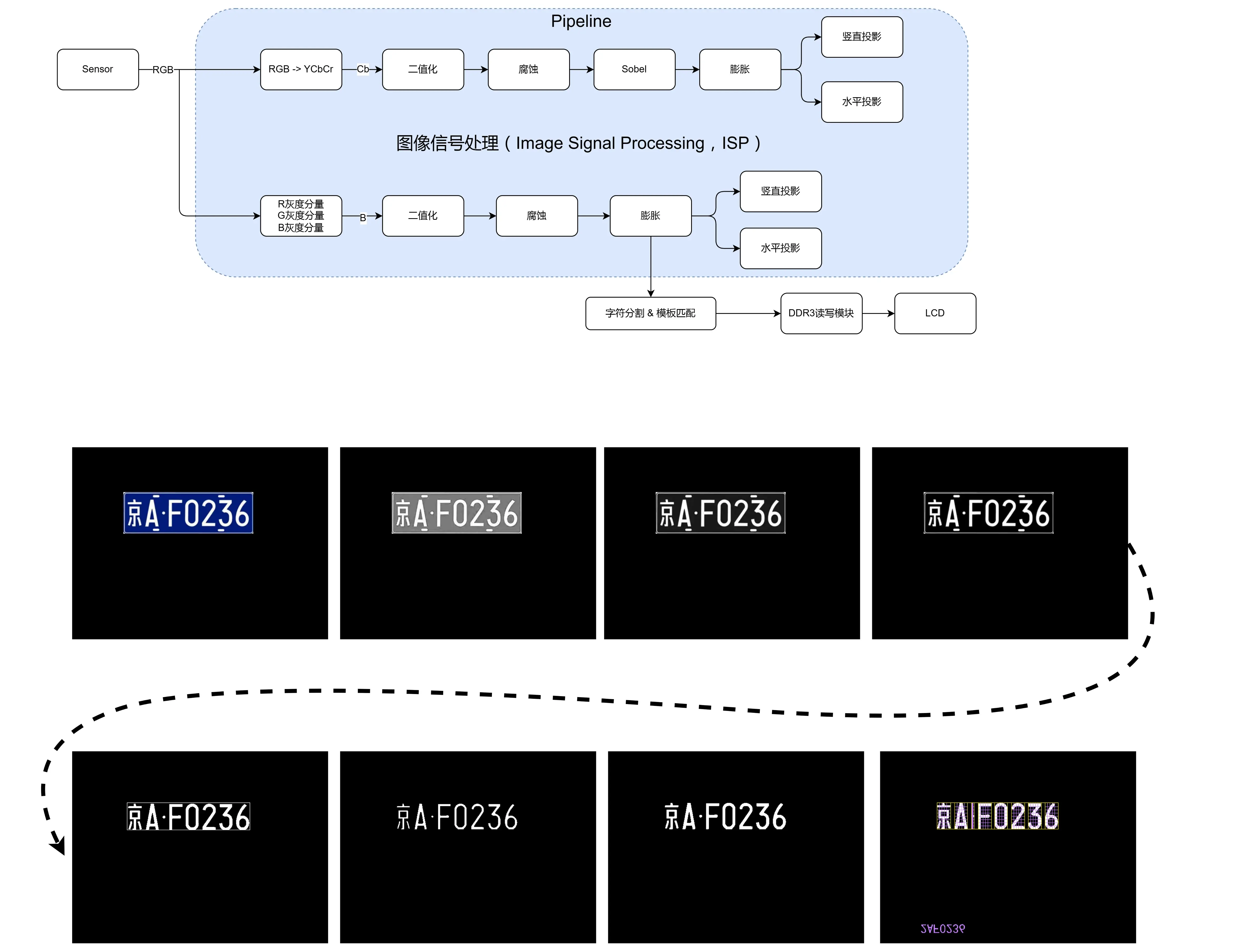

RISCV指令集在PulseRain Reindeer软核MCU于FPGA中的移植与设计方面的介绍如下PulseRain Reindeer软核MCU的FPGA移植划分平台相关部分包括PLLSDRAM厂商IPFPGA片上内存,以及特定于平台的配置独立部分包含硬件基础Bootloader和独立于平台的PulseRain Reindeer软核MCUReindeer软核的组成外围设备如UART。

上一篇: 直播间搭建,直播间搭建软件

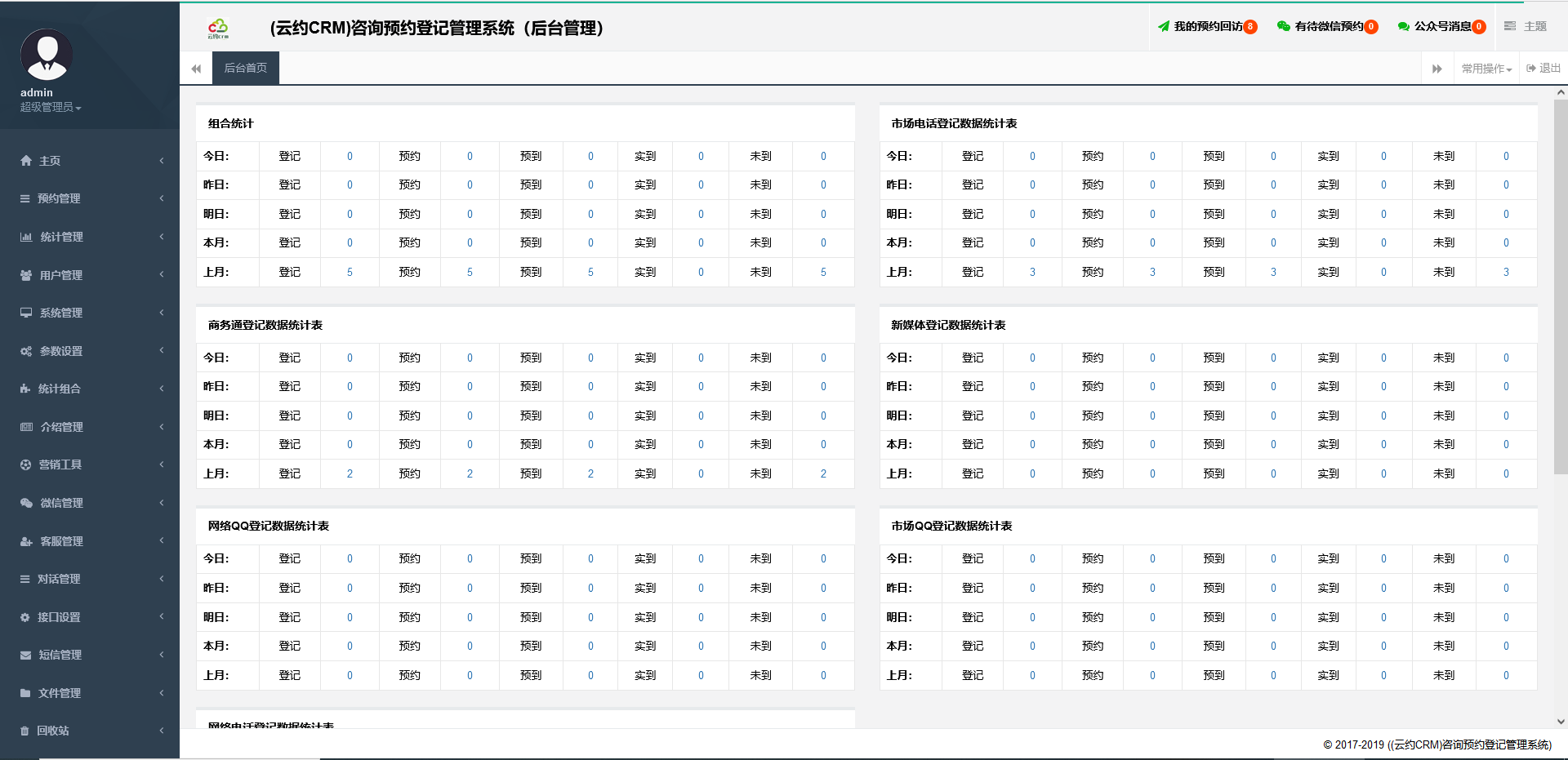

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

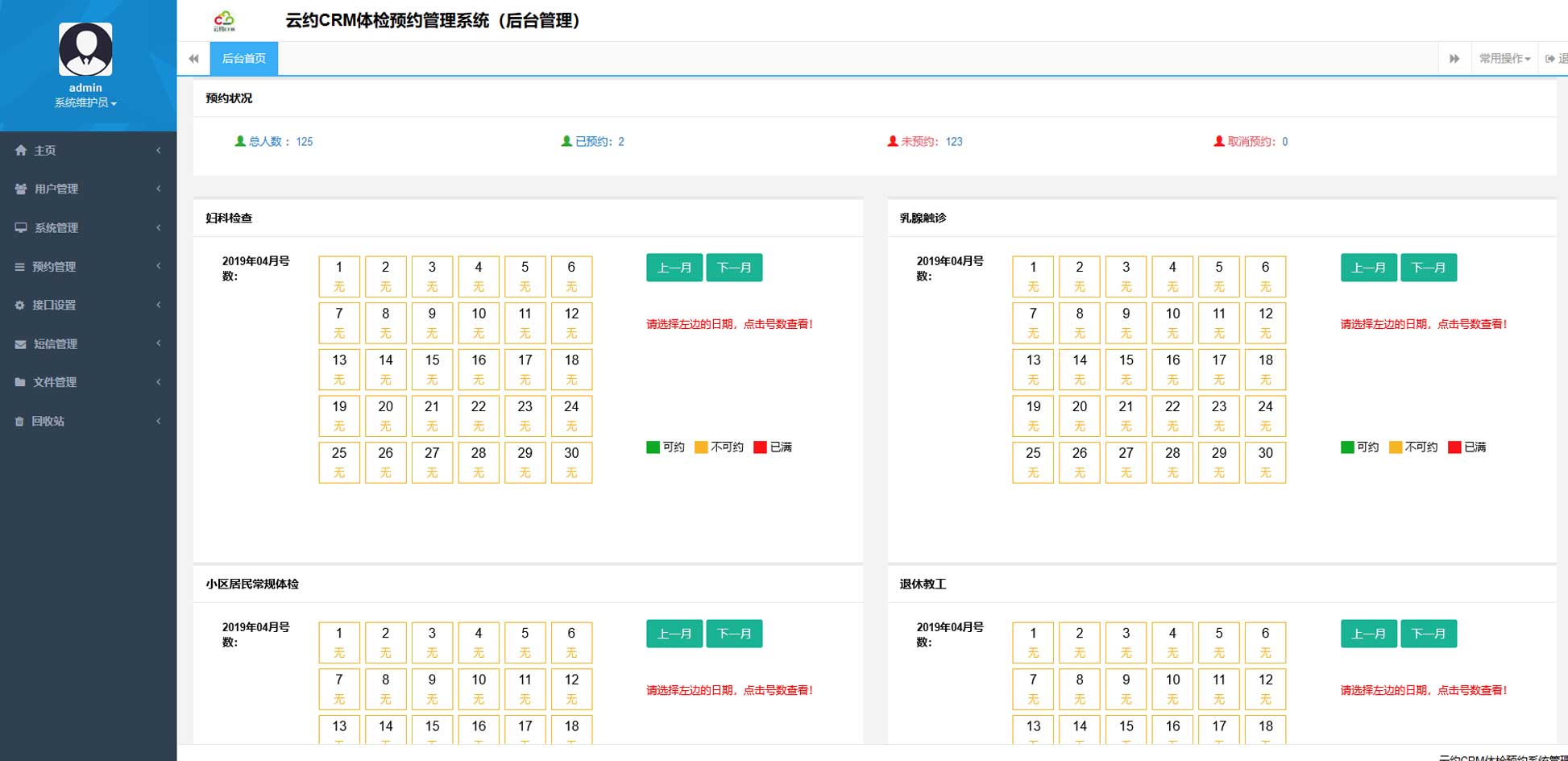

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

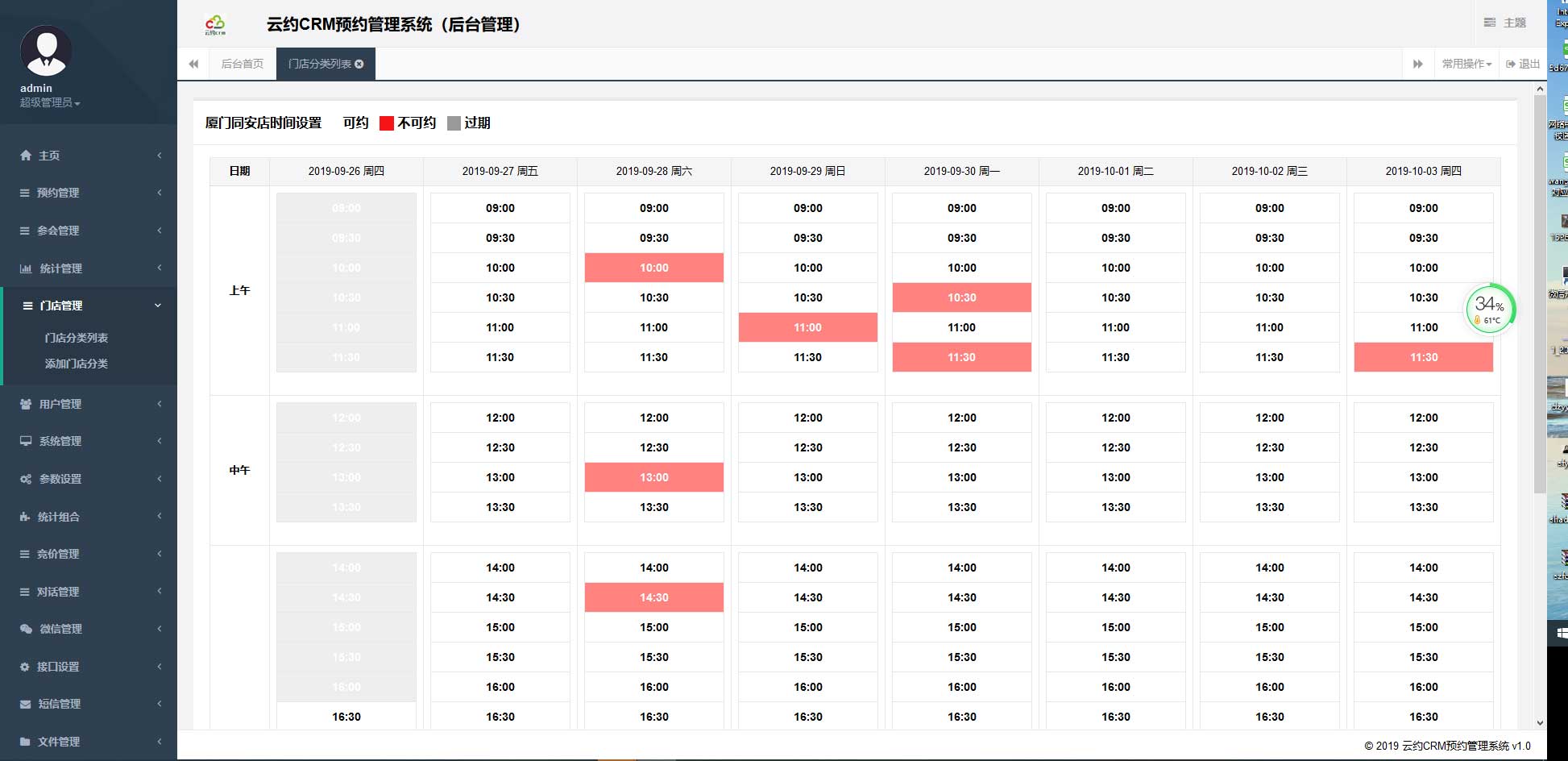

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com